## Safe Harbor

## **Forward Looking Statements**

We may make projections or other forward-looking statements regarding future events during our presentation today. We caution you that such statements are predictions based on information that is currently available and that actual results may differ materially. We refer you to the documents that the company has filed with the SEC, including our 10-K, 10-Qs and 8-Ks. These documents identify important risk factors that could cause actual results to differ materially from those contained in our projections or forward-looking statements.

#### **General Notice-Trademarks**

Lattice Semiconductor Corporation, Lattice Semiconductor (& design) and specific product designations are either registered trademarks or trademarks of Lattice Semiconductor Corporation or its subsidiaries in the United States and/or other countries.

Spartan is a registered trademark of Xilinx, Inc. and Cyclone is a registered trademark of Intel Corporation in the United States and/or other countries.

# **Solid Progress Over the Past Year**

#### **FOCUSED STRATEGY**

100% Focus on FPGA

#### **RE-ENERGIZED TEAM**

New Leadership Team; Revitalized Culture

## **SOLUTION INNOVATION**

**Application Focused** Innovation

#### **PROFIT EXPANSION**

2x Growth in Profit 5x Growth in Cash Flow

#### **INCREASED INVESTMENT**

Increasing Investment in **New Devices and Solutions**

#### **STRONGER ROADMAP**

Faster Cadence; **High Fidelity Execution**

Note: Net profit and cash flow expansion based on non-GAAP results from Q1 thru Q3 2019 compared to Q1 thru Q3 2018

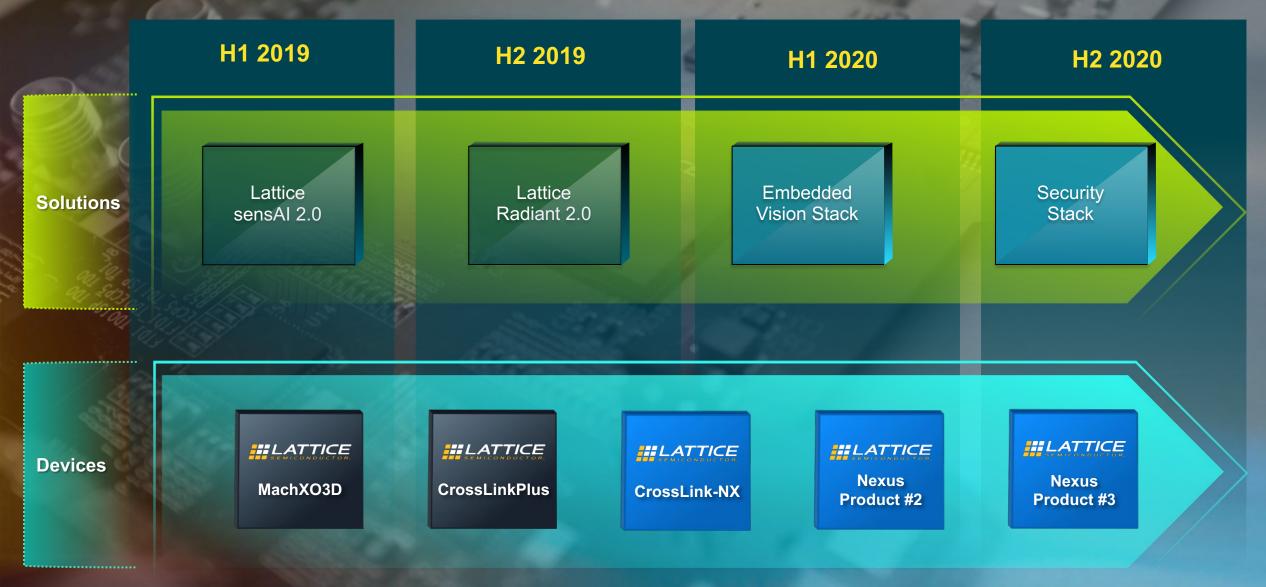

# **New Products Over the Next 12 Months**

New Al Capabilities

MAY 20, 2019

Robust Platform Security

LAUNCH DATE MAY 20, 2019

Enhanced Video Bridging

Sampling in H2 2019

Q3 2019

Next Generation FPGA Platform

Sampling early 2020

**Today**

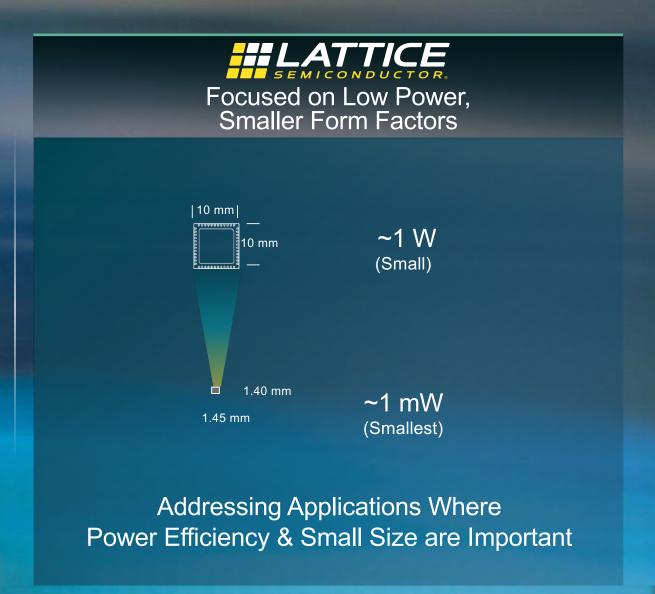

# Lattice's Focus: Low Power, Small Size

## OTHER FPGA COMPANIES

Focused on Large, High Power Devices for Data Center Compute

~200 W With Heat Sink

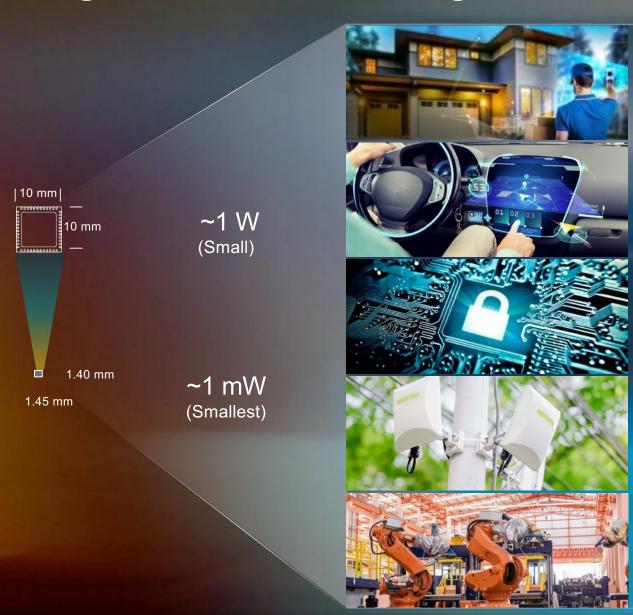

# **Solving Problems at the Edge**

## AI & IoT

Al Inferencing at the Edge

## **VIDEO**

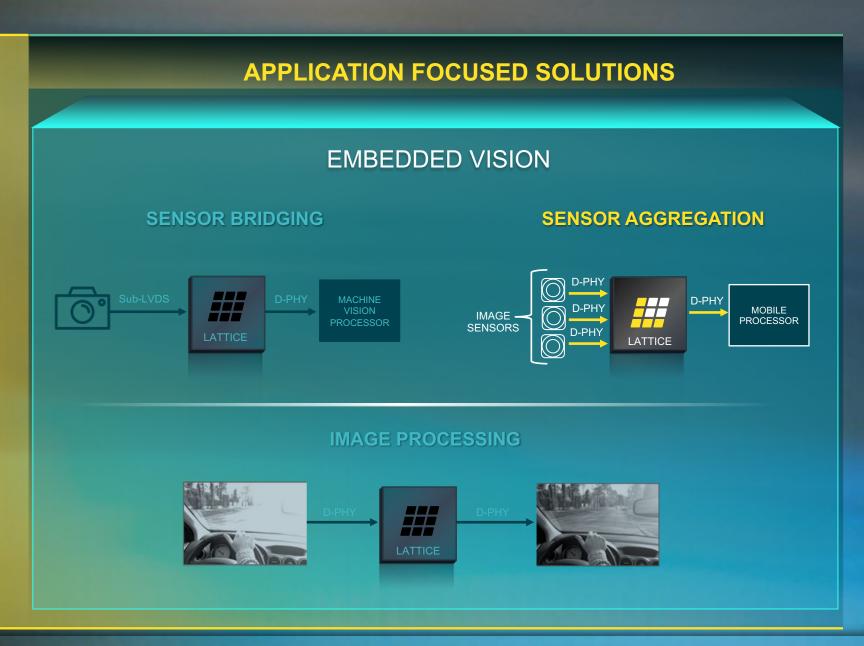

**Embedded Vision**

## **SECURITY**

Hardware Platform Security

## **5G INFRASTRUCTURE**

**Control & Management**

## **AUTOMATION**

Precision Robotic Motor Control

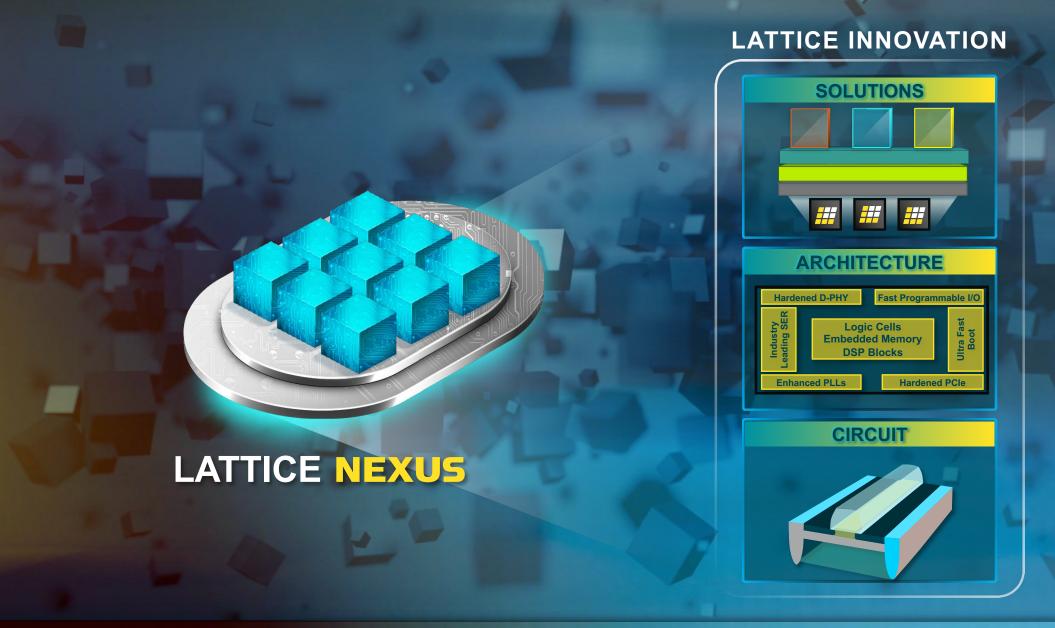

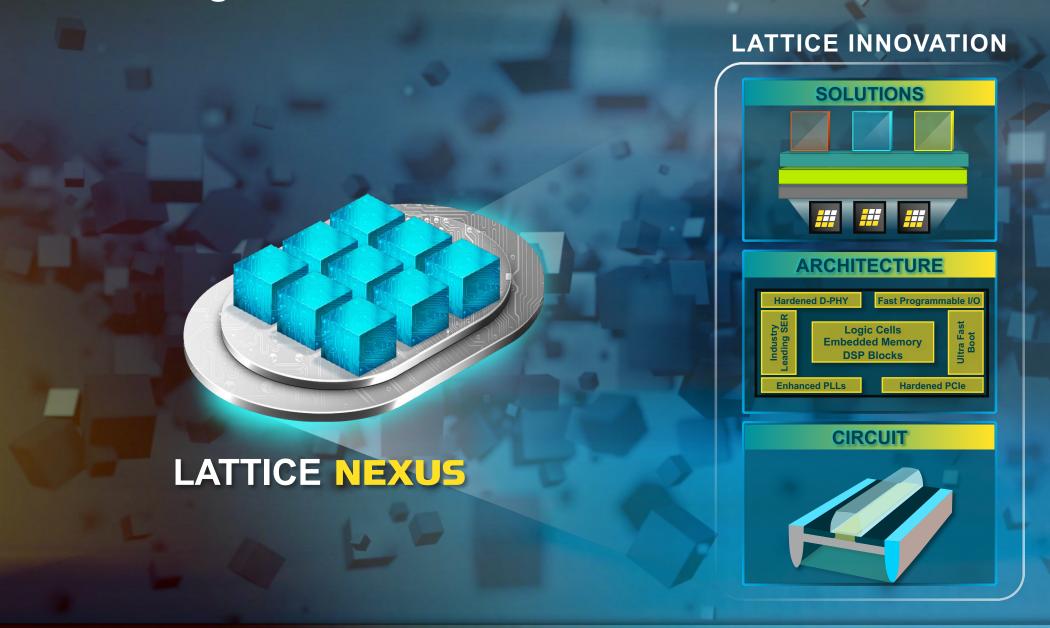

# **Introducing Our New Low Power FPGA Platform**

# Lattice Nexus is Changing the Landscape

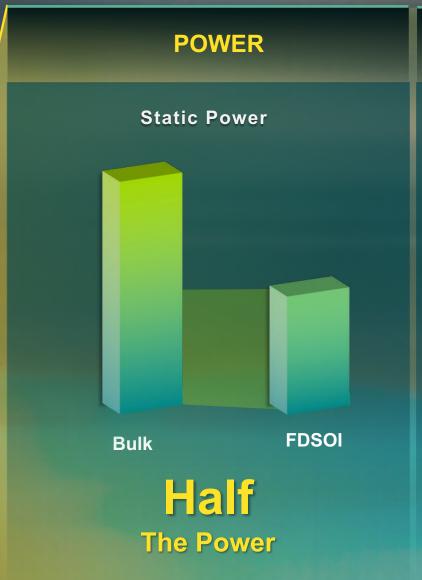

## **POWER**

## **PERFORMANCE**

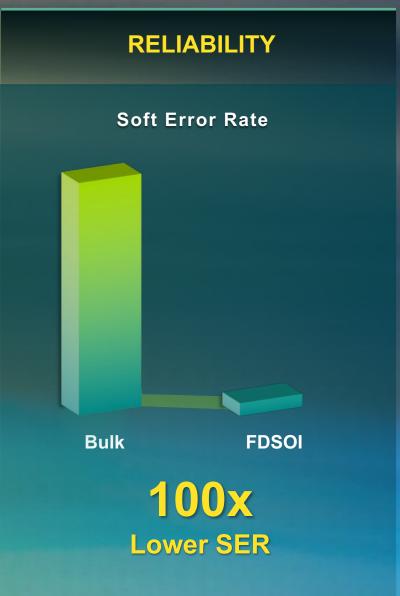

## **RELIABILITY**

# **Bringing Lattice Nexus Across All our Key End Markets**

5G Wireless

Switches/Routers

Servers

Client

Industrial IoT

**Factory Automation**

ADAS

Infotainment

**Smart Home**

Wearables

**\$3B Lattice Market Opportunity**

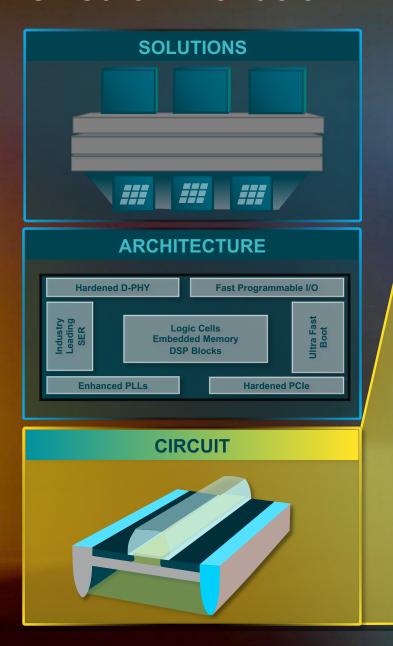

# LATTICE NEXUS

- Low power leadership

- Edge computing ready

- Robust and reliable

- Smallest form factor

- Faster innovation cadence

# **Steve Douglass**

Corporate Vice President, R&D

# **Introducing Our New Low Power FPGA Platform**

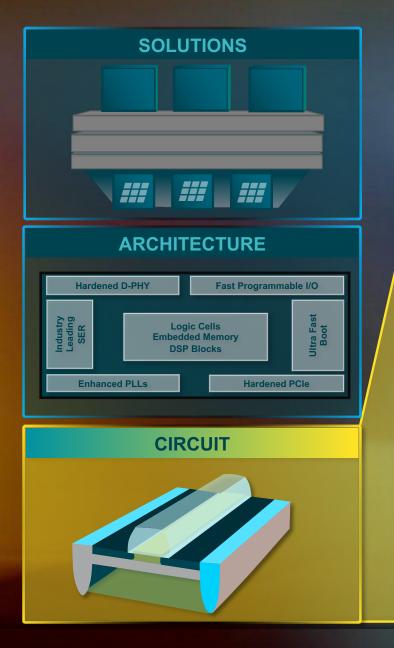

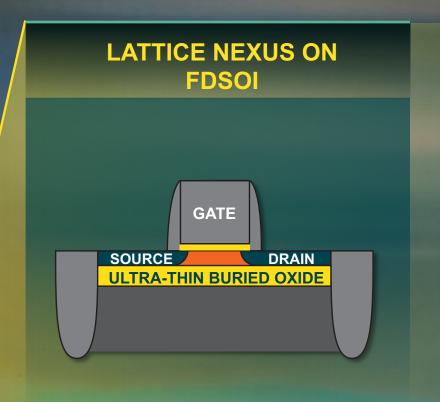

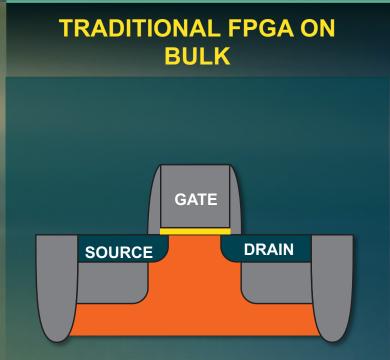

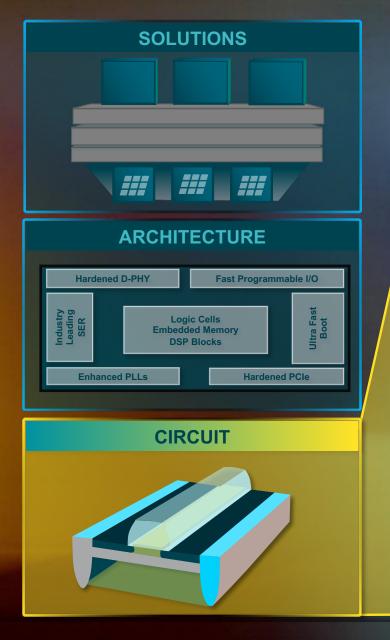

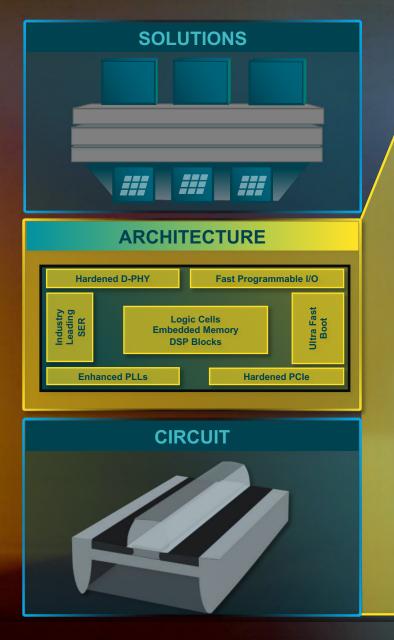

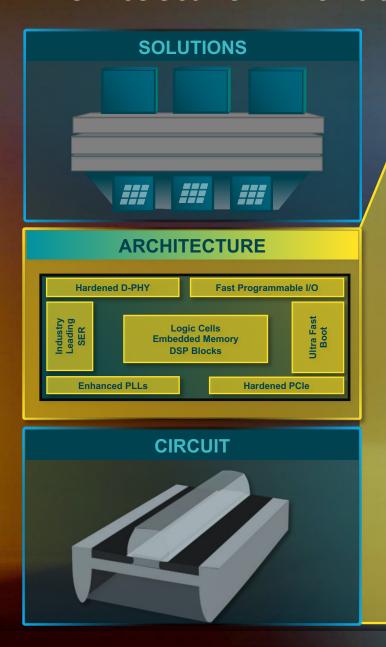

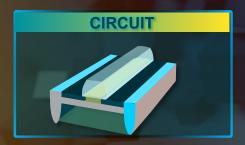

## **Circuit Innovation**

- Greatly reduces transistor leakage and susceptibility to soft errors

- FDSOI leverages bulk CMOS process and has fewer processing steps

- In high volume production today

# **Circuit Innovation**

# **Circuit Innovation**

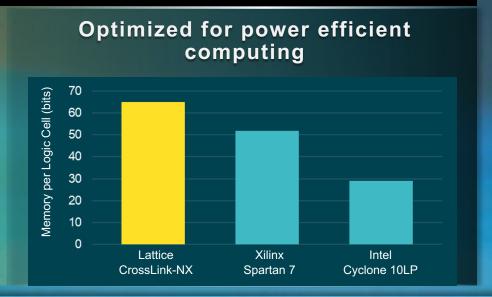

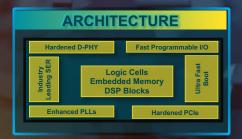

# **Architecture Innovation**

# **Architecture Innovation**

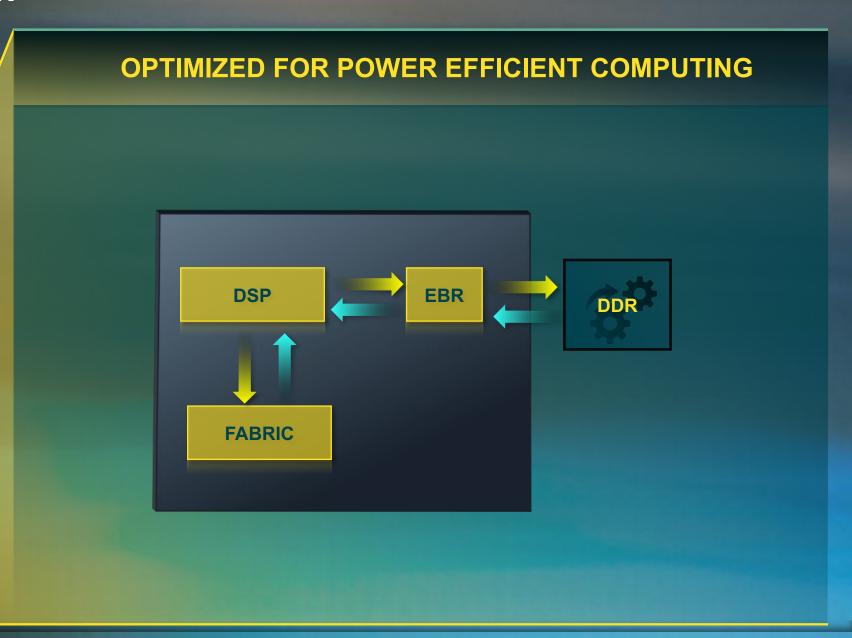

## **OPTIMIZED FOR POWER EFFICIENT COMPUTING**

**Faster Performance**

Half

The Power

Note: Performance and power relative to Lattice prior generation devices

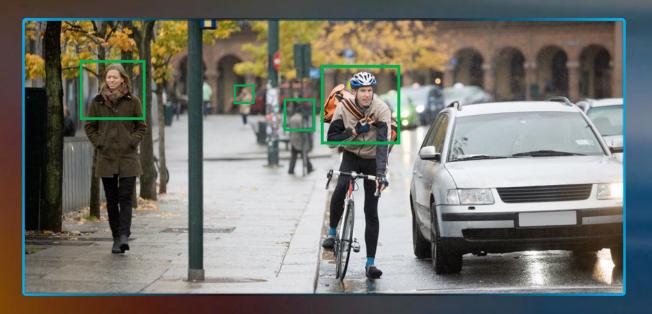

## **Human Presence Detection Demo**

#### **KEY APPLICATIONS**

Industrial safety

Security cameras

Client compute

Smart doorbells

#### **OVERVIEW**

## **What You Are Seeing**

Human presence detection with bounding box around upper body implemented with our first Lattice Nexus based device.

## **Why It Matters**

Human presence detection is a common AI use case in many Edge applications including security cameras, client compute, factory automation, and automotive.

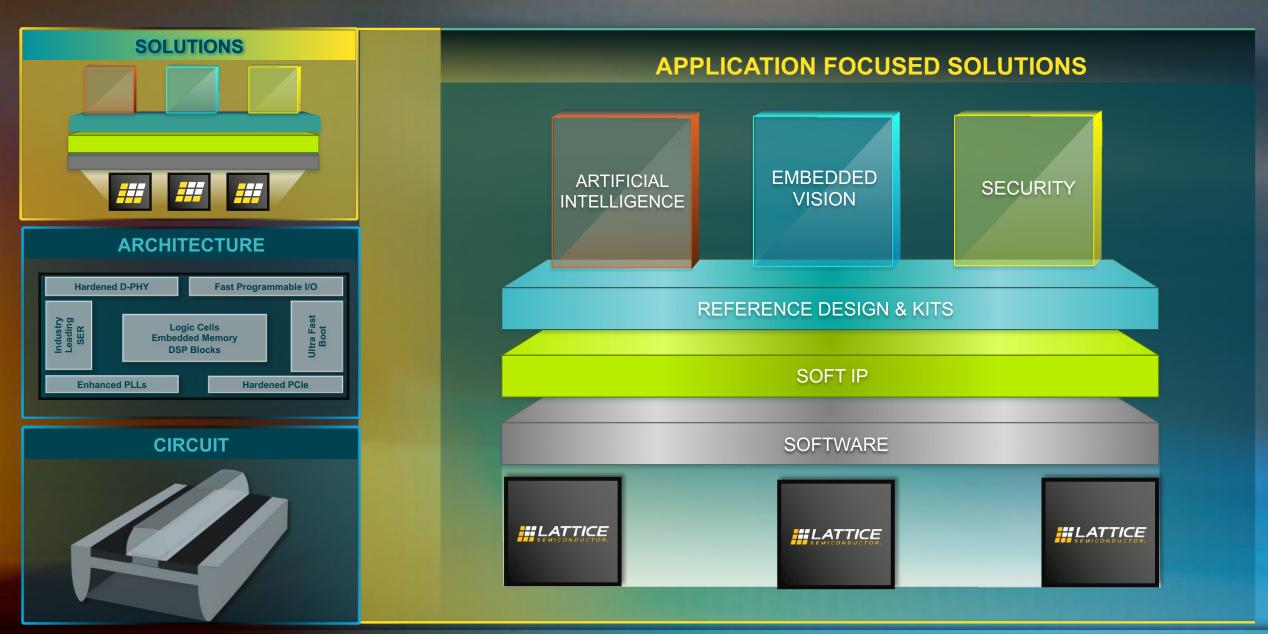

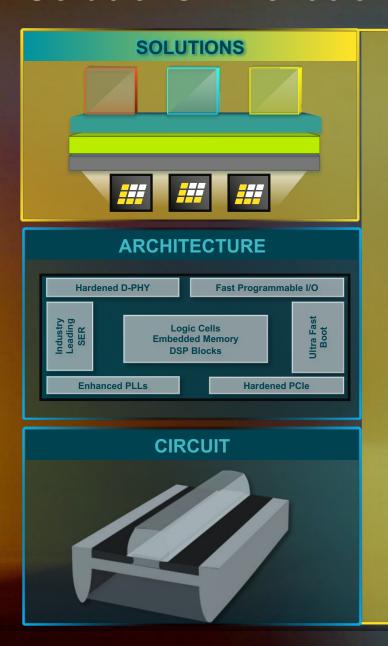

# **Solutions Innovation**

## **Solutions Innovation**

## **Solutions Innovation**

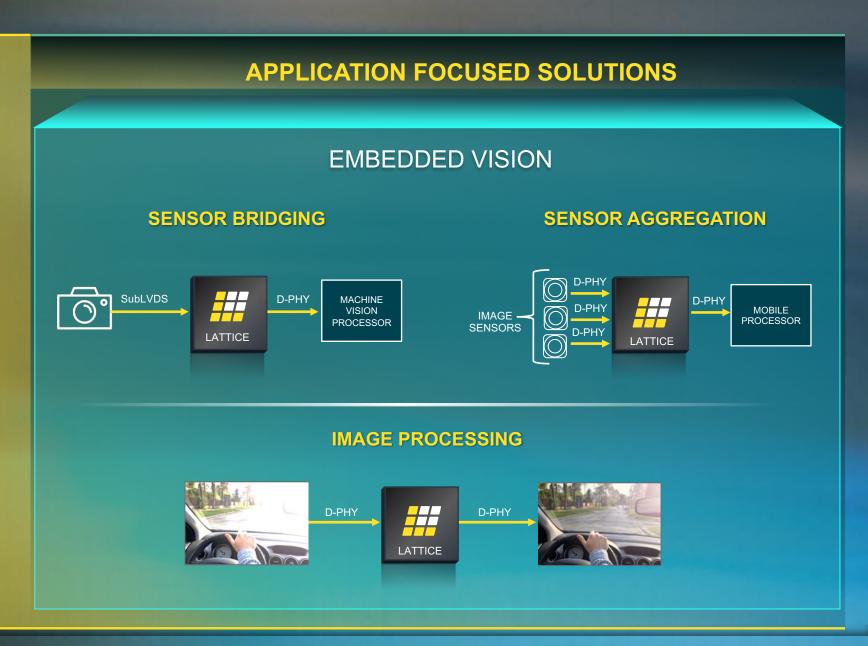

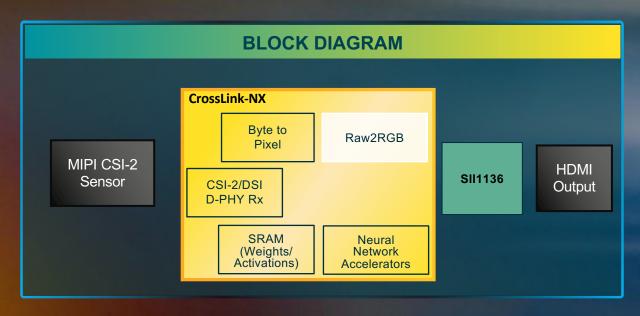

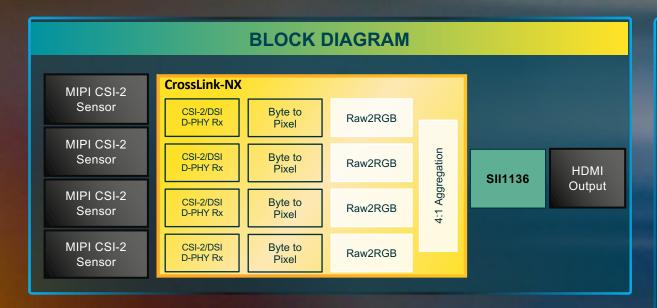

# **Camera Aggregation Demo**

#### **OVERVIEW**

## What You Are Seeing

MIPI CSI-2 data streams from 4 cameras are aggregated into a single data stream, bridged to parallel data and displayed in a single HDMI output.

## **Why It Matters**

Number of sensors are increasing, and the application processors have limited MIPI inputs.

Number of screen sizes and resolutions are increasing.

Need solution that can aggregate data streams for multiple image sensors in applications such as ADAS, drones, AR/VR, robots etc.

# **Introducing Our New Low Power FPGA Platform** LATTICE NEXUS Product N Product 3 Product 2 Product 1

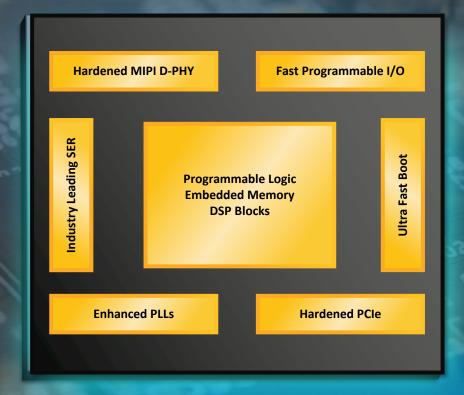

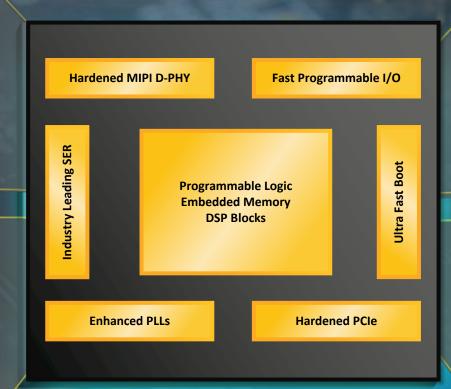

# **Introducing Lattice CrossLink-NX**

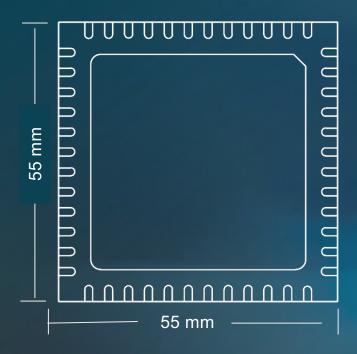

## A Closer Look at CrossLink-NX

027500

#### PROGRAMMABLE LOGIC CORE

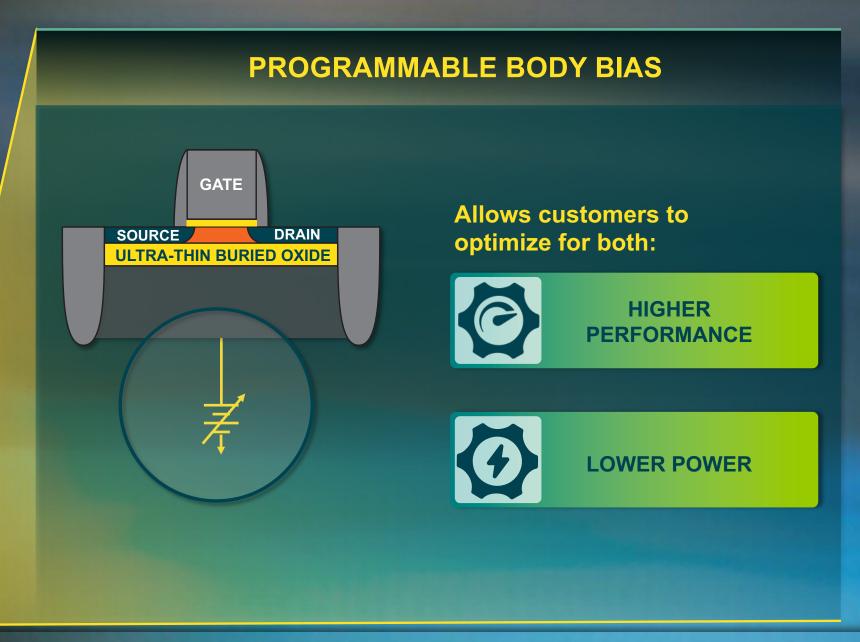

- Low power mode

- High performance mode

- High embedded memory count

- Optimized DSP blocks

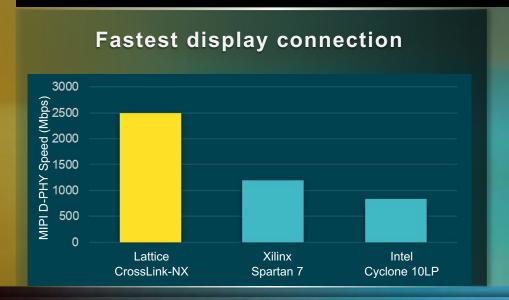

#### **DEDICATED INTERFACES**

- 8 D-PHY lanes @ 2.5 Gbps

- One lane PCle @ 5 Gbps

#### **FAST PROGRAMMABLE I/O**

- Up to 12 MIPI D-PHY interfaces @ 1.5 Gbps

- LVDS, subLVDS, SGMII

- DDR3 @ 1066 Mbps

- Up to 192 total I/O

#### **INSTANT-ON**

- 3 ms I/O configuration

- 14 ms device configuration

**Enhanced for Customer Needs: Power Efficiency, Performance, Reliability**

Esam Elashmawi

Chief Marketing & Strategy Officer

# **Customer Engagement**

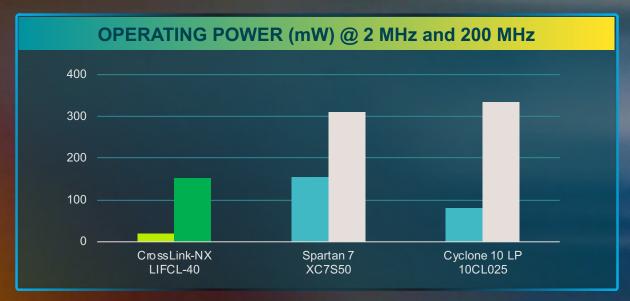

# Solving the Power Challenge

#### **PERFORMANCE**

#### **HIGH RELIABILITY**

#### **POWER IS KEY TO SOLVE**

## PORTABLE & AUTONOMOUS CHALLENGES

## **SYSTEM & OPERATING COSTS**

## **LOWEST POWER FPGA ...**

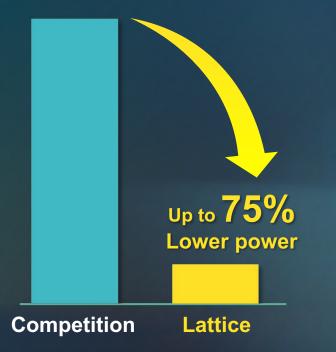

Up to 75% lower power compared to competition

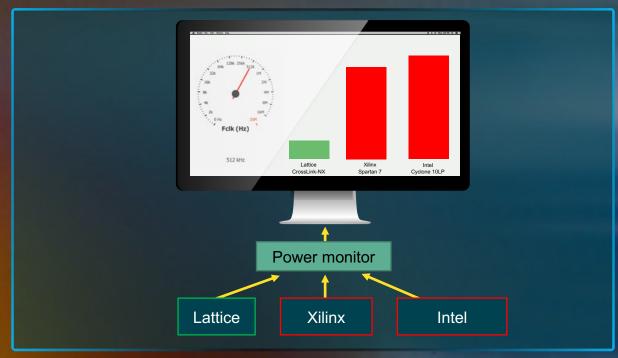

#### **Operating Power Consumption**

Xilinx

Spartan 7

Intel

Cyclone 10

Lattice

CrossLink-NX

## **CrossLink-NX Low Power Demo**

#### **OVERVIEW**

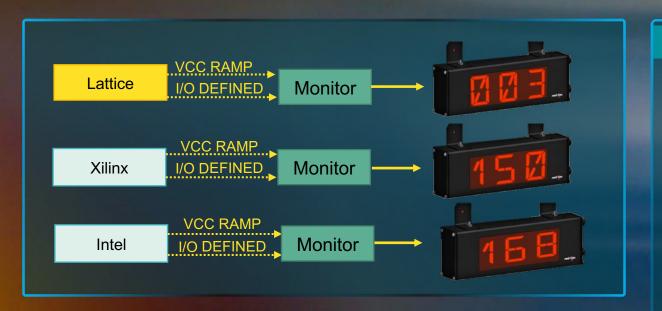

## **What You Are Seeing**

Power consumption for Lattice CrossLink-NX-40 running a typical design compared with Xilinx Spartan 7 (XC7S50) and Intel Cyclone 10LP (10CL025).

## **Why It Matters**

- Simplifies thermal management

- Improves operating costs

- Extends battery life

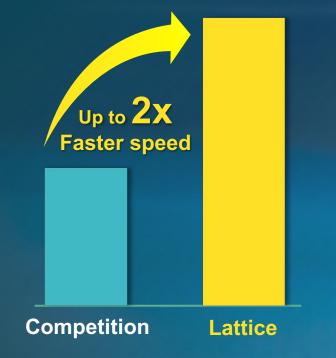

# Solving the Performance Challenge

PERFORMANCE

**HIGH RELIABILITY**

#### PERFORMANCE IS KEY TO SOLVE

## **ENHANCED PERFORMANCE FEATURES**

# sensAl Application Example: Retail Security Camera

# **ALWAYS-ON HUMAN COUNTING** SENSA **Lattice CrossLink-NX** Data **Sensors SRAM** Sensor (weights / activations) Interface Results **Neural Network Accelerators** MCU

# Instant-on

PERFORMANCE

**HIGH RELIABILITY**

## PERFORMANCE IS KEY TO SOLVE

## **INCREASED DEMAND FOR INSTANT-ON APPLICATIONS**

## **UP TO 50X FASTER**

Xilinx Spartan 7

Lattice CrossLink-NX

Instant-on Range

## **CrossLink-NX Instant-on Demo**

**Motor Control**

Human Machine Interfaces

**ADAS**

#### **OVERVIEW**

## What You Are Seeing

Time for device to self configure I/O to a user defined state for Lattice CrossLink-NX-40 compared with Xilinx Spartan 7 (XCS7-50) and Intel Cyclone 10LP (10LP025).

## Why It Matters

"Instant-on" I/O configuration is important for applications such as LED drivers, motor control and board housekeeping.

Reduces complexity, cost, and power dissipation of customer systems.

Note: based on competition's evaluation boards running at similar frequencies

# Solving the Reliability Challenge

#### **LOW POWER**

#### **PERFORMANCE**

#### HIGH RELIABILITY

#### **RELIABILITY IS KEY TO SOLVE**

#### **CRITICAL SAFETY & RUGGEDIZED**

#### **SYSTEM UP TIME**

#### **MOST RELIABLE FPGA FOR RUGGEDIZED APPS**

#### Temperature Ranges

- 40°C

125°C

Suitable for:

OUTDOOR | AUTOMOTIVE | INDUSTRIAL | AVIONICS

# Xilinx\* Spartan 7 Lattice CrossLink-NX FIT (Failure In Time) (1B device hours) \* Based on Xilinx published data

### **Small Size Matters** XILINX® Cyclone ® 10 15 mm SPARTAN<sub>®</sub>-7 ##LATTICE **#**LATTICE **##LATTICE** CrossLink-NX CrossLink-NX CrossLink-NX **←… 6 mm…**► **◄------** 15 mm ------**▼** 19 mm .... **CrossLink-NX** Xilinx Spartan 7 **Intel Cyclone 10LP**

LIFCL-40-7MG121C

40K

XC7S50-1GCSGA324C

50K

III LATTICE

10CL040YU484C6

40K

**Logic Cells**

WAYMO

## Jim Anderson

President, Chief Executive Officer

# **The Lowest Power FPGA Platform**

CrossLink-NX

**LOW POWER**

**PERFORMANCE**

# Faster Cadence of New Devices and Solutions

The Low Power Programmable Leader

# DEMO SIGNAGE

# **Human Presence Detection & Counting**

#### **OVERVIEW**

#### **What You Are Seeing**

Human presence detection and counting with bounding box around upper body implemented with Lattice CrossLink-NX

#### **Why It Matters**

Human presence detection is a common AI use case in many Edge applications including security cameras, client compute, factory automation, and automotive.

#### **The Lattice Advantage**

Lattice CrossLink-NX supports detection at 2x frame rate and 0.5x the power of prior generation

Lattice CrossLink-NX supports detection at 10x higher frame rate and 0.3x power compared to MCUs

Integrated D-PHY to reduce power and BOM cost

FPGA flexibility for additional pre/post processing compared to fixed function ASICs

# Camera Aggregation

#### **OVERVIEW**

#### What You Are Seeing

4 cameras, each providing a separate MIPI CSI-2 data stream aggregated into a single data stream, bridged to parallel data and displayed in a single HDMI output.

#### **Why It Matters**

Application processors with limited MIPI D-PHY inputs cannot interface to multiple image sensors in applications such as ADAS, drones, AR/VR, robots etc.

#### **The Lattice Advantage**

Only FPGA with up to 8 hard D-PHY lanes @ 2.5 Gbps

Scalable to support up to 14 MIPI D-PHY interfaces

Low power consumption ~300 mW

Up to 40K LUTs for customization and additional image processing

# **CrossLink-NX Delivering Up to 75% Lower Power**

#### **OVERVIEW**

#### **What You Are Seeing**

Power consumption for Lattice CrossLink-NX-40 running a typical design compared with Xilinx Spartan 7 (XC7S50) and Intel Cyclone 10LP (10CL025) running at a variety of frequencies

#### **Why It Matters**

Low power consumption simplifies thermal management, improves operating costs and where applicable extends battery life

#### **The Lattice Advantage**

Up to 75% lower power than Xilinx Spartan 7 and Intel Cyclone 10LP

Programmable back bias for per device performance / static power optimization

28 nm FD-SOI technology provides best in class dynamic power

HP and LP user modes

# CrossLink-NX Enabling Up to 50x Faster I/O Wake Up Time

# KEY APPLICATIONS Wotor Control Human Machine Interfaces ADAS

#### **OVERVIEW**

#### What You Are Seeing

The I/O self configuration time of the Lattice CrossLink-NX-40 running on the Lattice development board compared with Xilinx Spartan 7 (XCS7-50) and Intel Cyclone 10LP (10LP025) configured for the fastest possible configuration times on their associated development boards.

#### **Why It Matters**

"Instant-on" I/O configuration is important for applications such as LED drivers, motor control and board housekeeping.

Reduces complexity, cost, and power dissipation of customer systems

#### **The Lattice Advantage**

Smart monitor of SPI configuration memory avoids delay timers

150 MHz Quad SPI configuration interface for high speed configuration data transfer

Early I/O configuration ensures outputs stable as soon as possible